| Обноружение ошибок | ||||

| Исправление ошибок | ||||

| Коррекция ошибок | ||||

| Назад | ||||

Методы обнаружения ошибок

В обычном равномерном непомехоустойчивом коде число разрядов n в кодовых

комбинациях определяется числом сообщений и основанием кода.

Коды, у которых все кодовые комбинации разрешены, называются простыми или

равнодоступными и являются полностью безызбыточными. Безызбыточные коды обладают

большой «чувствительностью» к помехам. Внесение избыточности при использовании

помехоустойчивых кодов связано с увеличением n – числа разрядов кодовой комбинации. Таким

образом, все множество

подмножество разрешенных комбинаций, обладающих определенными признаками, и

подмножество запрещенных комбинаций, этими признаками не обладающих.

Помехоустойчивый код отличается от обычного кода тем, что в канал передаются не все

кодовые комбинации N, которые можно сформировать из имеющегося числа разрядов n, а только

их часть Nk , которая составляет подмножество разрешенных комбинаций. Если при приеме

выясняется, что кодовая комбинация принадлежит к запрещенным, то это свидетельствует о

наличии ошибок в комбинации, т.е. таким образом решается задача обнаружения ошибок. При

этом принятая комбинация не декодируется (не принимается решение о переданном

сообщении). В связи с этим помехоустойчивые коды называют корректирующими кодами.

Корректирующие свойства избыточных кодов зависят от правила их построения, определяющего

структуру кода, и параметров кода (длительности символов, числа разрядов, избыточности и т. п.).

Первые работы по корректирующим кодам принадлежат Хеммингу, который ввел понятие

минимального кодового расстояния dmin и предложил код, позволяющий однозначно указать ту

позицию в кодовой комбинации, где произошла ошибка. К информационным элементам k в коде

Хемминга добавляется m проверочных элементов для автоматического определения

местоположения ошибочного символа. Таким образом, общая длина кодовой комбинации

составляет: n = k + m.

Метричное представление n,k-кодов

В настоящее время наибольшее внимание с точки зрения технических приложений

уделяется двоичным блочным корректирующим кодам. При использовании блочных кодов

цифровая информация передается в виде отдельных кодовых комбинаций (блоков) равной

длины. Кодирование и декодирование каждого блока осуществляется независимо друг от друга.

Почти все блочные коды относятся к разделимым кодам, кодовые комбинации которых

состоят из двух частей: информационной и проверочной. При общем числе n символов в блоке

число информационных символов равно k, а число проверочных символов:

К основным характеристикам корректирующих кодов относятся:

|

— число разрешенных и запрещенных кодовых комбинаций; |

Для блочных двоичных кодов, с числом символов в блоках, равным n, общее число

возможных кодовых комбинаций определяется значением

Число разрешенных кодовых комбинаций при наличии k информационных разрядов в

первичном коде:

Очевидно, что число запрещенных комбинаций:

а с учетом отношение будет

где m – число избыточных (проверочных) разрядов в блочном коде.

Избыточностью корректирующего кода называют величину

откуда следует:

Эта величина показывает, какую часть общего числа символов кодовой комбинации

составляют информационные символы. В теории кодирования величину Bk называют

относительной скоростью кода. Если производительность источника информации равна H

символов в секунду, то скорость передачи после кодирования этой информации будет

поскольку в закодированной последовательности из каждых n символов только k символов

являются информационными.

Если число ошибок, которые нужно обнаружить или исправить, значительно, то необходимо

иметь код с большим числом проверочных символов. Чтобы при этом скорость передачи

оставалась достаточно высокой, необходимо в каждом кодовом блоке одновременно

увеличивать как общее число символов, так и число информационных символов.

При этом длительность кодовых блоков будет существенно возрастать, что приведет к

задержке информации при передаче и приеме. Чем сложнее кодирование, тем длительнее

временная задержка информации.

Минимальное кодовое расстояние – dmin. Для того чтобы можно было обнаружить и

исправлять ошибки, разрешенная комбинация должна как можно больше отличаться от

запрещенной. Если ошибки в канале связи действуют независимо, то вероятность преобразования

одной кодовой комбинации в другую будет тем меньше, чем большим числом символов они

различаются.

Если интерпретировать кодовые комбинации как точки в пространстве, то отличие

выражается в близости этих точек, т. е. в расстоянии между ними.

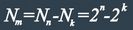

Количество разрядов (символов), которыми отличаются две кодовые комбинации, можно

принять за кодовое расстояние между ними. Для определения этого расстояния нужно сложить

две кодовые комбинации «по модулю 2» и подсчитать число единиц в полученной сумме.

Например, две кодовые комбинации xi = 01011 и xj = 10010 имеют расстояние d(xi,xj) , равное 3,

так как:

Здесь под операцией ⊕ понимается сложение «по модулю 2».

Заметим, что кодовое расстояние d(xi,x0) между комбинацией xi и нулевой x0 = 00…0

называют весом W комбинации xi, т.е. вес xi равен числу «1» в ней.

Расстояние между различными комбинациями некоторого конкретного кода могут

существенно отличаться. Так, в частности, в безызбыточном первичном натуральном коде n = k это

расстояние для различных комбинаций может изменяться от единицы до величины n, равной

разрядности кода. Особую важность для характеристики корректирующих свойств кода имеет

минимальное кодовое расстояние dmin, определяемое при попарном сравнении всех кодовых

комбинаций, которое называют расстоянием Хемминга.

В безызбыточном коде все комбинации являются разрешенными и его минимальное

кодовое расстояние равно единице – dmin=1. Поэтому достаточно исказиться одному символу,

чтобы вместо переданной комбинации была принята другая разрешенная комбинация. Чтобы код

обладал корректирующими свойствами, необходимо ввести в него некоторую избыточность,

которая обеспечивала бы минимальное расстояние между любыми двумя разрешенными

комбинациями не менее двух – dmin ≥ 2..

Минимальное кодовое расстояние является важнейшей характеристикой помехоустойчивых

кодов, указывающей на гарантируемое число обнаруживаемых или исправляемых заданным

кодом ошибок.

Число обнаруживаемых или исправляемых ошибок

При применении двоичных кодов учитывают только дискретные искажения, при которых

единица переходит в нуль («1» → «0») или нуль переходит в единицу («0» → «1»). Переход «1» →

«0» или «0» → «1» только в одном элементе кодовой комбинации называют единичной ошибкой

(единичным искажением). В общем случае под кратностью ошибки подразумевают число

позиций кодовой комбинации, на которых под действием помехи одни символы оказались

замененными на другие. Возможны двукратные (g = 2) и многократные (g > 2) искажения

элементов в кодовой комбинации в пределах 0 ≤ g ≤ n.

Минимальное кодовое расстояние является основным параметром, характеризующим

корректирующие способности данного кода. Если код используется только для обнаружения

ошибок кратностью g0, то необходимо и достаточно, чтобы минимальное кодовое расстояние

было равно dmin ≥ g0 + 1.

В этом случае никакая комбинация из go ошибок не может перевести одну разрешенную

кодовую комбинацию в другую разрешенную. Таким образом, условие обнаружения всех ошибок

кратностью g0 можно записать

Чтобы можно было исправить все ошибки кратностью gu и менее, необходимо иметь

минимальное расстояние, удовлетворяющее условию dmin ≥ 2gu

В этом случае любая кодовая комбинация с числом ошибок gu отличается от каждой

разрешенной комбинации не менее чем в gu+1 позициях. Если условие не выполнено,

возможен случай, когда ошибки кратности g исказят переданную комбинацию так, что она станет

ближе к одной из разрешенных комбинаций, чем к переданной или даже перейдет в другую

разрешенную комбинацию. В соответствии с этим, условие исправления всех ошибок кратностью

не более gи можно записать:

Из и

следует, что если код исправляет все ошибки кратностью gu, то число

ошибок, которые он может обнаружить, равно go = 2gu. Следует отметить, что эти соотношения

устанавливают лишь гарантированное минимальное число обнаруживаемых или

исправляемых ошибок при заданном dmin и не ограничивают возможность обнаружения ошибок

большей кратности. Например, простейший код с проверкой на четность с dmin = 2 позволяет

обнаруживать не только одиночные ошибки, но и любое нечетное число ошибок в пределах go < n.

Корректирующие возможности кодов

Вопрос о минимально необходимой избыточности, при которой код обладает нужными

корректирующими свойствами, является одним из важнейших в теории кодирования. Этот вопрос

до сих пор не получил полного решения. В настоящее время получен лишь ряд верхних и нижних

оценок (границ), которые устанавливают связь между максимально возможным минимальным

расстоянием корректирующего кода и его избыточностью.

Коды Хэмминга

Построение кодов Хемминга базируется на принципе проверки на четность веса W (числа

единичных символов «1») в информационной группе кодового блока.

Поясним идею проверки на четность на примере простейшего корректирующего кода,

который так и называется кодом с проверкой на четность или кодом с проверкой по паритету

(равенству).

В таком коде к кодовым комбинациям безызбыточного первичного двоичного k-разрядного

кода добавляется один дополнительный разряд (символ проверки на четность, называемый

проверочным, или контрольным). Если число символов «1» исходной кодовой комбинации

четное, то в дополнительном разряде формируют контрольный символ «0», а если число

символов «1» нечетное, то в дополнительном разряде формируют символ «1». В результате

общее число символов «1» в любой передаваемой кодовой комбинации всегда будет четным.

Таким образом, правило формирования проверочного символа сводится к следующему:

где i – соответствующий информационный символ («0» или «1»); k – общее их число а, под

операцией ⊕ здесь и далее понимается сложение «по модулю 2». Очевидно, что добавление

дополнительного разряда увеличивает общее число возможных комбинаций вдвое по сравнению

с числом комбинаций исходного первичного кода, а условие четности разделяет все комбинации

на разрешенные и неразрешенные. Код с проверкой на четность позволяет обнаруживать

одиночную ошибку при приеме кодовой комбинации, так как такая ошибка нарушает условие

четности, переводя разрешенную комбинацию в запрещенную.

Критерием правильности принятой комбинации является равенство нулю результата S

суммирования «по модулю 2» всех n символов кода, включая проверочный символ m1. При

наличии одиночной ошибки S принимает значение 1:

— ошибок нет,

— однократная ошибка

Этот код является (k+1,k)-кодом, или (n,n–1)-кодом. Минимальное расстояние кода равно

двум (dmin = 2), и, следовательно, никакие ошибки не могут быть исправлены. Простой код с

проверкой на четность может использоваться только для обнаружения (но не исправления)

однократных ошибок.

Увеличивая число дополнительных проверочных разрядов, и формируя по определенным

правилам проверочные символы m, равные «0» или «1», можно усилить корректирующие

свойства кода так, чтобы он позволял не только обнаруживать, но и исправлять ошибки. На этом и

основано построение кодов Хемминга.

Коды Хемминга позволяют исправлять одиночную ошибку, с помощью непосредственного

описания. Для каждого числа проверочных символов m =3, 4, 5… существует классический код

Хемминга с маркировкой

т.е. (7,4), (15,11) (31,26) …

При других значениях числа информационных символов k получаются так называемые

усеченные (укороченные) коды Хемминга. Так для кода имеющего 5 информационных символов,

потребуется использование корректирующего кода (9,5), являющегося усеченным от

классического кода Хемминга (15,11), так как число символов в этом коде уменьшается

(укорачивается) на 6.

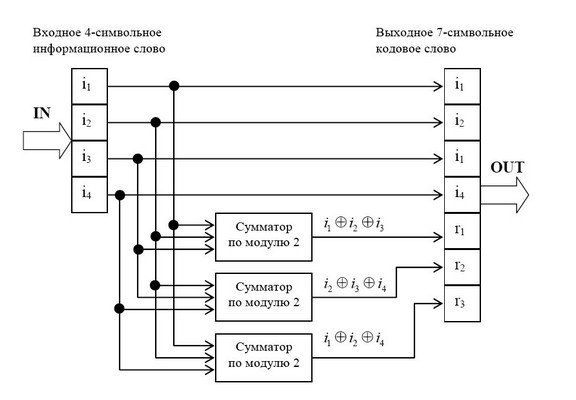

Для примера рассмотрим классический код Хемминга (7,4), который можно сформировать и

описать с помощью кодера, представленного на рис. 1 В простейшем варианте при заданных

четырех информационных символах: i1, i2, i3, i4 (k = 4), будем полагать, что они сгруппированы в

начале кодового слова, хотя это и не обязательно. Дополним эти информационные символы

тремя проверочными символами (m = 3), задавая их следующими равенствами проверки на

четность, которые определяются соответствующими алгоритмами, где знак ⊕ означает

сложение «по модулю 2»: r1 = i1 ⊕ i2 ⊕ i3, r2 = i2 ⊕ i3 ⊕ i4, r3 = i1 ⊕ i2 ⊕ i4.

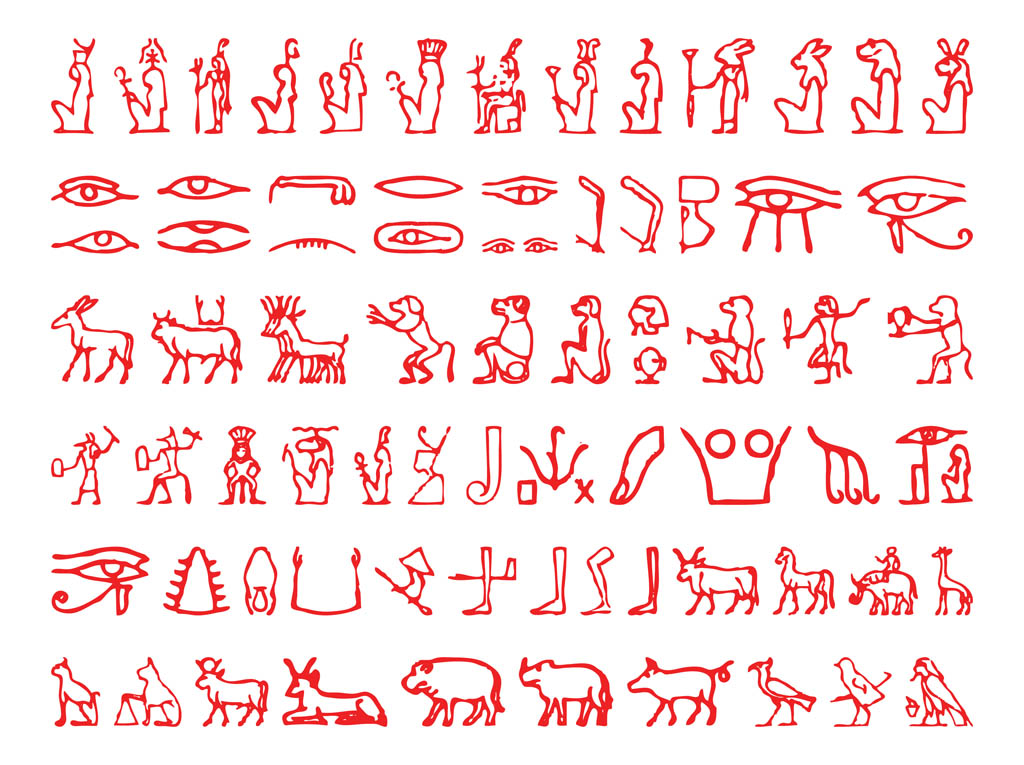

В соответствии с этим алгоритмом определения значений проверочных символов mi, в табл.

1 выписаны все возможные 16 кодовых слов (7,4)-кода Хемминга.

Таблица 1 Кодовые слова (7,4)-кода Хэмминга

|

k=4 |

m=4 |

|

i1 i2 i3 i4 |

r1 r2 r3 |

|

0 0 0 0 |

0 0 0 |

|

0 0 0 1 |

0 1 1 |

|

0 0 1 0 |

1 1 0 |

|

0 0 1 1 |

1 0 1 |

|

0 1 0 0 |

1 1 1 |

|

0 1 0 1 |

1 0 0 |

|

0 1 1 0 |

0 0 1 |

|

0 1 1 1 |

0 1 0 |

|

1 0 0 0 |

1 0 1 |

|

1 0 0 1 |

1 0 0 |

|

1 0 1 0 |

0 1 1 |

|

1 0 1 1 |

0 0 0 |

|

1 1 0 0 |

0 1 0 |

|

1 1 0 1 |

0 0 1 |

|

1 1 1 0 |

1 0 0 |

|

1 1 1 1 |

1 1 1 |

На рис.1 приведена блок-схема кодера – устройства автоматически кодирующего

информационные разряды в кодовые комбинации в соответствии с табл.1

Рис. 1 Кодер для (7,4)-кода Хемминга

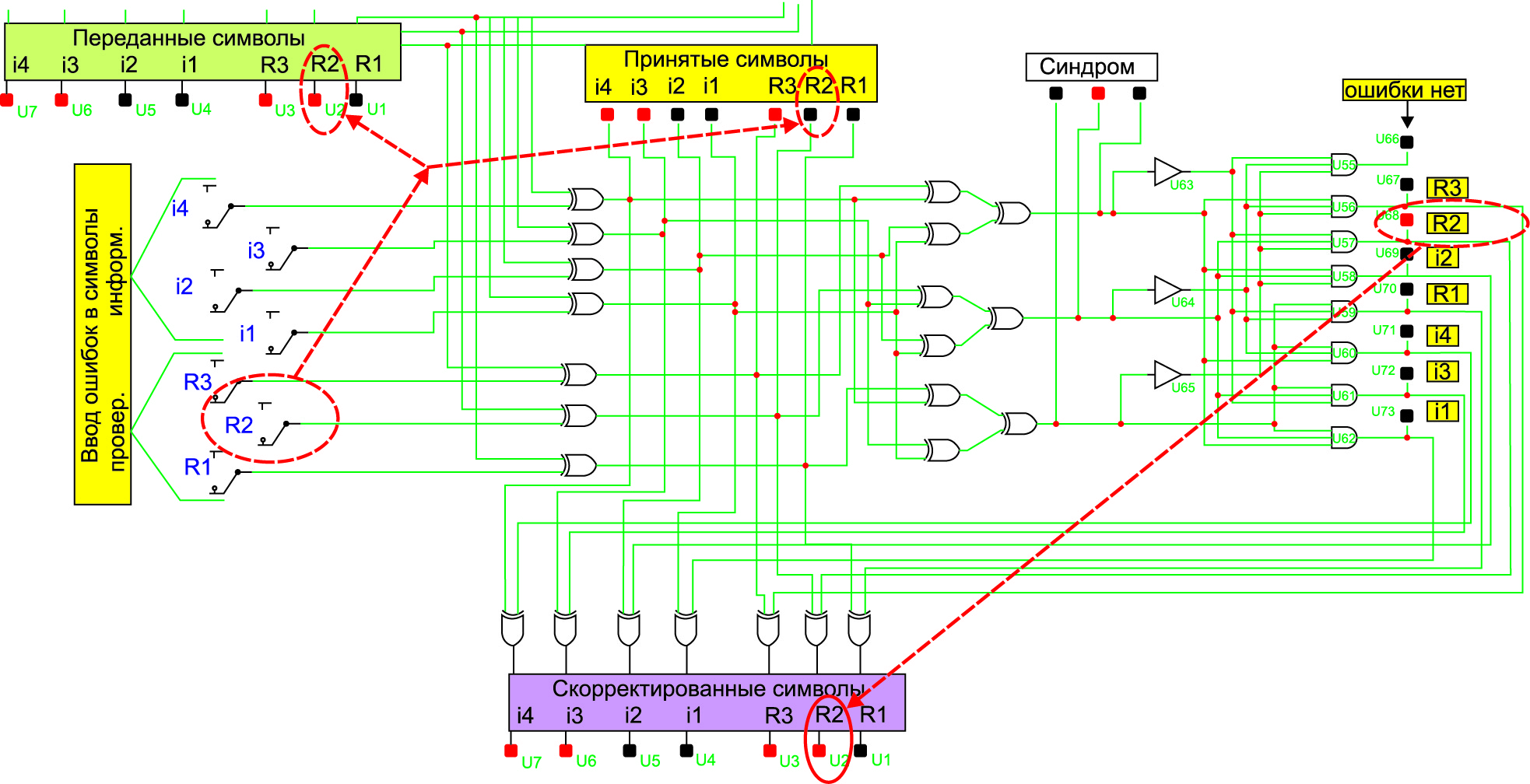

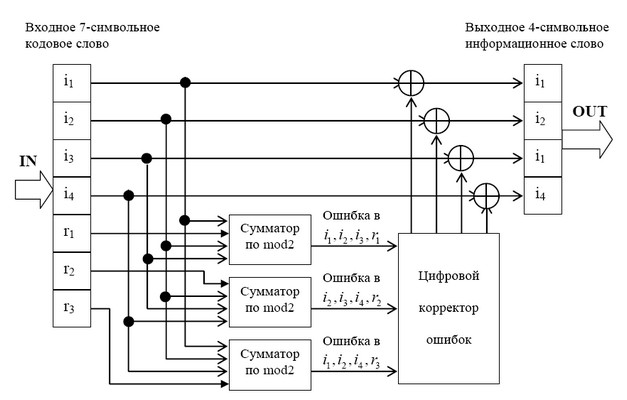

На рис. 1.4 приведена схема декодера для (7,4) – кода Хемминга, на вход которого

поступает кодовое слово

. Апостроф означает, что любой символ слова может

быть искажен помехой в телекоммуникационном канале.

В декодере в режиме исправления ошибок строится последовательность:

Трехсимвольная последовательность (s1, s2, s3) называется синдромом. Термин «синдром»

используется и в медицине, где он обозначает сочетание признаков, характерных для

определенного заболевания. В данном случае синдром S = (s1, s2, s3) представляет собой

сочетание результатов проверки на четность соответствующих символов кодовой группы и

характеризует определенную конфигурацию ошибок (шумовой вектор).

Число возможных синдромов определяется выражением:

При числе проверочных символов m =3 имеется восемь возможных синдромов (23 =

Нулевой синдром (000) указывает на то, что ошибки при приеме отсутствуют или не обнаружены.

Всякому ненулевому синдрому соответствует определенная конфигурация ошибок, которая и

исправляется. Классические коды Хемминга имеют число синдромов, точно равное их

необходимому числу (что позволяет исправить все однократные ошибки в любом информативном

и проверочном символах) и включают один нулевой синдром. Такие коды называются

плотноупакованными.

Усеченные коды являются неплотноупакованными, так как число синдромов у них

превышает необходимое. Так, в коде (9,5) при четырех проверочных символах число синдромов

будет равно 24 =16, в то время как необходимо всего 10. Лишние 6 синдромов свидетельствуют о

неполной упаковке кода (9,5).

Рис. 2 Декодер для (7, 4)-кода Хемминга

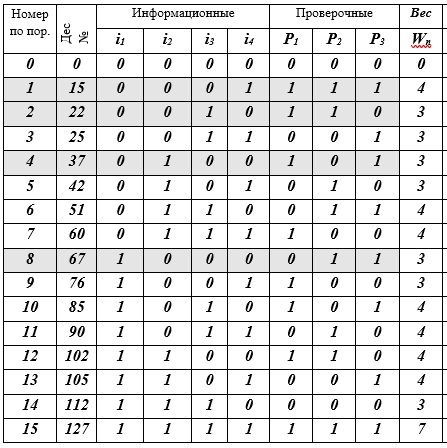

Для рассматриваемого кода (7,4) в табл. 2 представлены ненулевые синдромы и

соответствующие конфигурации ошибок.

Таблица 2 Синдромы (7, 4)-кода Хемминга

|

Синдром |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|

Конфигурация ошибок |

0000001 |

0000010 |

0000100 |

0001000 |

0010000 |

0100000 |

1000000 |

|

Ошибка в символе |

m1 |

m2 |

i4 |

m1 |

i1 |

i3 |

i2 |

Таким образом, (7,4)-код позволяет исправить все одиночные ошибки. Простая проверка

показывает, что каждая из ошибок имеет свой единственный синдром. При этом возможно

создание такого цифрового корректора ошибок (дешифратора синдрома), который по

соответствующему синдрому исправляет соответствующий символ в принятой кодовой группе.

После внесения исправления проверочные символы ri можно на выход декодера (рис. 2) не

выводить. Две или более ошибок превышают возможности корректирующего кода Хемминга, и

декодер будет ошибаться. Это означает, что он будет вносить неправильные исправления и

выдавать искаженные информационные символы.

Идея построения подобного корректирующего кода, естественно, не меняется при

перестановке позиций символов в кодовых словах. Все такие варианты также называются (7,4)-

кодами Хемминга.

Циклические коды

Своим названием эти коды обязаны такому факту, что для них часть комбинаций, либо все

комбинации могут быть получены путем циклическою сдвига одной или нескольких базовых

комбинаций кода.

Построение такого кода основывается на использовании неприводимых многочленов в поле

двоичных чисел. Такие многочлены не могут быть представлены в виде произведения

многочленов низших степеней подобно тому, как простые числа не могут быть представлены

произведением других чисел. Они делятся без остатка только на себя или на единицу.

Для определения неприводимых многочленов раскладывают на простые множители бином

хn -1. Так, для n = 7 это разложение имеет вид:

(x7)=(x-1)(x3+x2)(x3+x-1)

Каждый из полученных множителей разложения может применяться для построения

корректирующего кода.

Неприводимый полином g(x) называют задающим, образующим или порождающим

для корректирующего кода. Длина n (число разрядов) создаваемого кода произвольна.

Кодовая последовательность (комбинация) корректирующего кода состоит из к информационных

разрядов и n — к контрольных (проверочных) разрядов. Степень порождающего полинома

r = n — к равна количеству неинформационных контрольных разрядов.

Если из сделанного выше разложения (при n = 7) взять полипом (х — 1), для которого

r=1, то k=n-r=7-1=6. Соответствующий этому полиному код используется для контроля

на чет/нечет (обнаружение ошибок). Для него минимальное кодовое расстояние D0 = 2

(одна единица от D0 — для исходного двоичного кода, вторая единица — за счет контрольного разряда).

Если же взять полином (x3+x2+1) из указанного разложения, то степень полинома

r=3, а k=n-r=7-3=4.

Контрольным разрядам в комбинации для некоторого кода могут быть четко определено место (номера разрядов).

Тогда код называют систематическим или разделимым. В противном случае код является неразделимым.

Способы построения циклических кодов по заданному полиному.

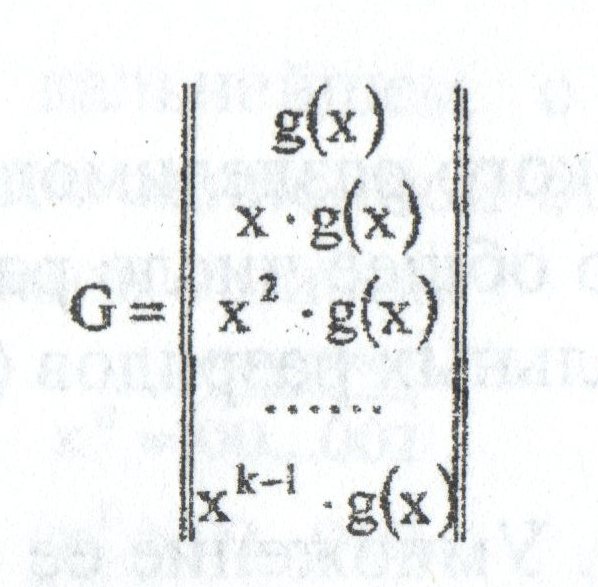

1) На основе порождающей (задающей) матрицы G, которая имеет n столбцов, k строк, то есть параметры которой

связаны с параметрами комбинаций кода. Порождающую матрицу строят, взяв в качестве ее строк порождающий

полином g(x) и (k — 1) его циклических сдвигов:

Пример; Определить порождающую матрицу, если известно, что n=7, k=4, задающий полином g(x)=x3+х+1.

Решение: Кодовая комбинация, соответствующая задающему полиному g(x)=x3+х+1, имеет вид 1011.

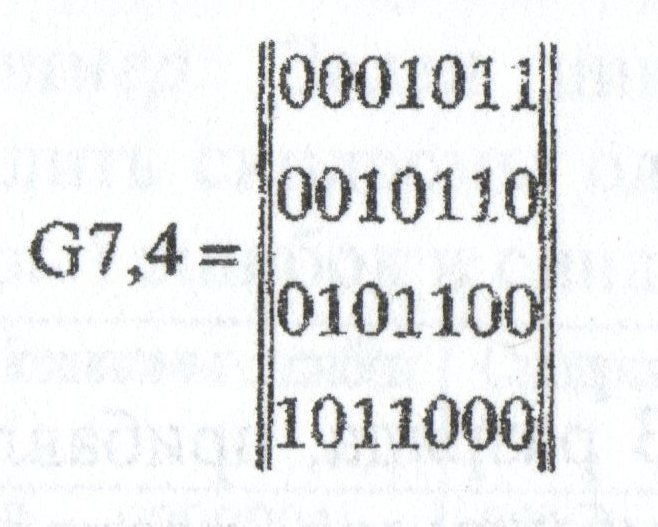

Тогда порождающая матрица G7,4 для кода при n=7, к=4 с учетом того, что k-1=3, имеет вид:

Порождающая матрица содержит k разрешенных кодовых комбинаций. Остальные комбинации кода,

количество которых (2k — k) можно определить суммированием по модулю 2 всевозможных сочетаний

строк матрицы Gn,k. Для матрицы, полученной в приведенном выше примере, суммирование по модулю 2

четырех строк 1-2, 1-3, 1-4, 2-3, 2-4, 3-4 дает следующие кодовые комбинации циклического кода:

001110101001111010011011101010011101110100

Другие комбинации искомого корректирующего кода могут быть получены сложением трех комбинаций, например,

из сочетания строк 1-3-4, что дает комбинацию 1111111, а также сложением четырех строк 1-2-3-4, что

дает комбинацию 1101001 и т.д.

Ряд комбинаций искомого кода может быть получено путем дальнейшего циклического сдвига комбинаций

порождающей матрицы, например, 0110001, 1100010, 1000101. Всего для образования искомого циклического

кода требуется 2k=24=16 комбинаций.

2) Умножение исходных двоичных кодовых комбинаций на задающий полином.

Исходными комбинациями являются все k-разрядные двоичные комбинации. Так, например, для исходной

комбинации 1111 (при k = 4) умножение ее на задающий полином g(x)=x3+х+1=1011 дает 1101001.

Полученные на основе двух рассмотренных способов циклические коды не являются разделимыми.

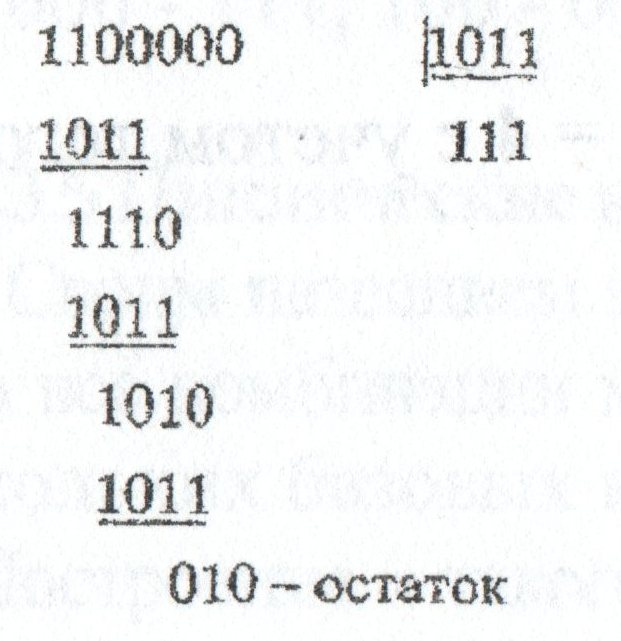

3) Деление на задающий полином.

Для получения разделимого (систематического) циклического кода необходимо разделить многочлен

xn-k*h(x), где h(x) — исходная двоичная комбинация, на задающий полином g(x) и прибавить полученный

остаток от деления к многочлену xn-k*h(x).

Заметим, что умножение исходной комбинации h(x) на xn-k эквивалентно сдвигу h(x) на (n-к) разрядов влево.

Пример: Требуется определить комбинации циклического разделимого кода, заданного полиномом g(x)=x3+х+1=1011 и

имеющего общее число разрядов 7, число информационных разрядов 4, число контрольных разрядов (n-k)=3.

Решение: Пусть исходная комбинация h(x)=1100. Умножение ее на xn-k=x3=1000 дает

x3*(x3+x2)=1100000, то есть эквивалентно

сдвигу исходной комбинации на 3 разряда влево. Деление комбинации 1100000 на комбинацию 1011, эквивалентно задающему полиному, дает:

Полученный остаток от деления, содержащий xn-k=3 разряда, прибавляем к полиному, в результате чего получаем искомую комбинацию

разделимого циклического кода: 1100010. В ней 4 старших разряда (слева) соответствуют исходной двоичной комбинации, а три младших

разряда являются контрольными.

Следует сделать ряд указаний относительно процедуры деления:

1) При делении задающий полином совмещается старшим разрядом со старшим «единичными разрядом делимого.

2) Вместо вычитания по модулю 2 выполняется эквивалентная ему процедура сложения по модулю 2.

3) Деление продолжается до тех пор, пока степень очередного остатка не будет меньше степени делителя (задающего полинома). При достижении

этого полученный остаток соответствует искомому содержанию контрольных разрядов для данной искомой двоичной комбинации.

Для проверки правильности выполнения процедуры определения комбинации циклического кода необходимо разделить полученную комб1шацию на задающий полином с

учетом сделанных выше замечаний. Получение нулевого остатка от такого деления свидетельствует о правильности определения комбинации.

Логический код 4В/5В

Логический код 4В/5В заменяет исходные символы длиной в 4 бита на символы длиной в 5 бит. Так как результирующие символы содержат избыточные биты, то

общее количество битовых комбинаций в них больше, чем в исходных. Таким образом, пяти-битовая схема дает 32 (25) двухразрядных буквенно-цифровых символа,

имеющих значение в десятичном коде от 00 до 31. В то время как исходные данные могут содержать только четыре бита или 16 (24) символов.

Поэтому в результирующем коде можно подобрать 16 таких комбинаций, которые не содержат большого количества нулей, а остальные считать запрещенными кодами

(code violation). В этом случае длинные последовательности нулей прерываются, и код становится самосинхронизирующимся для любых передаваемых данных.

Исчезает также постоянная составляющая, а значит, еще более сужается спектр сигнала. Но этот метод снижает полезную пропускную способность линии,

так как избыточные единицы пользовательской информации не несут, и только «занимают эфирное время». Избыточные коды позволяют приемнику распознавать

искаженные биты. Если приемник принимает запрещенный код, значит, на линии произошло искажение сигнала.

Итак, рассмотрим работу логического кода 4В/5В. Преобразованный сигнал имеет 16 значений для передачи информации и 16 избыточных значений. В декодере

приемника пять битов расшифровываются как информационные и служебные сигналы.

Для служебных сигналов отведены девять символов, семь символов — исключены.

Исключены комбинации, имеющие более трех нулей (01 — 00001, 02 — 00010, 03 — 00011, 08 — 01000, 16 — 10000). Такие сигналы интерпретируются символом

V и командой приемника VIOLATION — сбой. Команда означает наличие ошибки из-за высокого уровня помех или сбоя передатчика. Единственная

комбинация из пяти нулей (00 — 00000) относится к служебным сигналам, означает символ Q и имеет статус QUIET — отсутствие сигнала в линии.

Такое кодирование данных решает две задачи — синхронизации и улучшения помехоустойчивости. Синхронизация происходит за счет исключения

последовательности более трех нулей, а высокая помехоустойчивость достигается приемником данных на пяти-битовом интервале.

Цена за эти достоинства при таком способе кодирования данных — снижение скорости передачи полезной информации.

К примеру, В результате добавления одного избыточного бита на четыре информационных, эффективность использования полосы

частот в протоколах с кодом MLT-3 и кодированием данных 4B/5B уменьшается соответственно на 25%.

Схема кодирования 4В/5В представлена в таблице.

|

Двоичный код 4В |

Результирующий код 5В |

|

0 0 0 0 |

1 1 1 1 0 |

|

0 0 0 1 |

0 1 0 0 1 |

|

0 0 1 0 |

1 0 1 0 0 |

|

0 0 1 1 |

1 0 1 0 1 |

|

0 1 0 0 |

0 1 0 1 0 |

|

0 1 0 1 |

0 1 0 1 1 |

|

0 1 1 0 |

0 1 1 1 0 |

|

0 1 1 1 |

0 1 1 1 1 |

|

1 0 0 0 |

1 0 0 1 0 |

|

1 0 0 1 |

1 0 0 1 1 |

|

1 0 1 0 |

1 0 1 1 0 |

|

1 0 1 1 |

1 0 1 1 1 |

|

1 1 0 0 |

1 1 0 1 0 |

|

1 1 0 1 |

1 1 0 1 1 |

|

1 1 1 0 |

1 1 1 0 0 |

|

1 1 1 1 |

1 1 1 0 1 |

Итак, соответственно этой таблице формируется код 4В/5В, затем передается по линии с помощью физического кодирования по

одному из методов потенциального кодирования, чувствительному только к длинным последовательностям нулей — например, в помощью

цифрового кода NRZI.

Символы кода 4В/5В длиной 5 бит гарантируют, что при любом их сочетании на линии не могут встретиться более трех нулей подряд.

Буква ^ В в названии кода означает, что элементарный сигнал имеет 2 состояния — от английского binary — двоичный. Имеются

также коды и с тремя состояниями сигнала, например, в коде 8В/6Т для кодирования 8 бит исходной информации используется

код из 6 сигналов, каждый из которых имеет три состояния. Избыточность кода 8В/6Т выше, чем кода 4В/5В, так как на 256

исходных кодов приходится 36=729 результирующих символов.

Как мы говорили, логическое кодирование происходит до физического, следовательно, его осуществляют оборудование канального

уровня сети: сетевые адаптеры и интерфейсные блоки коммутаторов и маршрутизаторов. Поскольку, как вы сами убедились,

использование таблицы перекодировки является очень простой операцией, поэтому метод логического кодирования избыточными

кодами не усложняет функциональные требования к этому оборудованию.

Единственное требование — для обеспечения заданной пропускной способности линии передатчик, использующий избыточный код,

должен работать с повышенной тактовой частотой. Так, для передачи кодов 4В/5В со скоростью 100 Мб/с передатчик должен

работать с тактовой частотой 125 МГц. При этом спектр сигнала на линии расширяется по сравнению со случаем, когда по

линии передается чистый, не избыточный код. Тем не менее, спектр избыточного потенциального кода оказывается уже

спектра манчестерского кода, что оправдывает дополнительный этап логического кодирования, а также работу приемника

и передатчика на повышенной тактовой частоте.

В основном для локальных сетей проще, надежней, качественней, быстрей — использовать логическое кодирование данных

с помощью избыточных кодов, которое устранит длительные последовательности нулей и обеспечит синхронизацию

сигнала, потом на физическом уровне использовать для передачи быстрый цифровой код NRZI, нежели без предварительного

логического кодирования использовать для передачи данных медленный, но самосинхронизирующийся манчестерский код.

Например, для передачи данных по линии с пропускной способностью 100М бит/с и полосой пропускания 100 МГц,

кодом NRZI необходимы частоты 25 — 50 МГц, это без кодирования 4В/5В. А если применить для NRZI еще и

кодирование 4В/5В, то теперь полоса частот расширится от 31,25 до 62,5 МГц. Но тем не менее, этот диапазон

еще «влазит» в полосу пропускания линии. А для манчестерского кода без применения всякого дополнительного

кодирования необходимы частоты от 50 до 100 МГц, и это частоты основного сигнала, но они уже не будут пропускаться

линией на 100 МГц.

Скрэмблирование

Другой метод логического кодирования основан на предварительном «перемешивании» исходной информации таким

образом, чтобы вероятность появления единиц и нулей на линии становилась близкой.

Устройства, или блоки, выполняющие такую операцию, называются скрэмблерами (scramble — свалка, беспорядочная сборка) .

При скремблировании данные перемешиваються по определенному алгоритму и приемник, получив двоичные данные, передает

их на дескрэмблер, который восстанавливает исходную последовательность бит.

Избыточные биты при этом по линии не передаются.

Суть скремблирования заключается просто в побитном изменении проходящего через систему потока данных. Практически

единственной операцией, используемой в скремблерах является XOR — «побитное исключающее ИЛИ», или еще говорят —

сложение по модулю 2. При сложении двух единиц исключающим ИЛИ отбрасывается старшая единица и результат записывается — 0.

Метод скрэмблирования очень прост. Сначала придумывают скрэмблер. Другими словами придумывают по какому соотношению

перемешивать биты в исходной последовательности с помощью «исключающего ИЛИ». Затем согласно этому соотношению из текущей

последовательности бит выбираются значения определенных разрядов и складываются по XOR между собой. При этом все разряды

сдвигаются на 1 бит, а только что полученное значение («0» или «1») помещается в освободившийся самый младший разряд.

Значение, находившееся в самом старшем разряде до сдвига, добавляется в кодирующую последовательность, становясь очередным

ее битом. Затем эта последовательность выдается в линию, где с помощью методов физического кодирования передается к

узлу-получателю, на входе которого эта последовательность дескрэмблируется на основе обратного отношения.

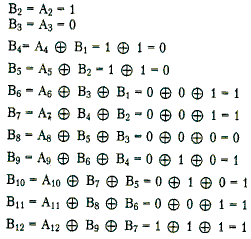

Например, скрэмблер может реализовывать следующее соотношение:

где Bi — двоичная цифра результирующего кода, полученная на i-м такте работы скрэмблера, Ai — двоичная цифра исходного

кода, поступающая на i-м такте на вход скрэмблера, Bi-3 и Bi-5 — двоичные цифры результирующего кода, полученные на

предыдущих тактах работы скрэмблера, соответственно на 3 и на 5 тактов ранее текущего такта, ⊕ — операция исключающего

ИЛИ (сложение по модулю 2).

Теперь давайте, определим закодированную последовательность, например, для такой исходной последовательности 110110000001.

Скрэмблер, определенный выше даст следующий результирующий код:

B1=А1=1 (первые три цифры результирующего кода будут совпадать с исходным, так как еще нет нужных предыдущих цифр)

Таким образом, на выходе скрэмблера появится последовательность 110001101111. В которой нет последовательности из шести нулей, п

рисутствовавшей в исходном коде.

После получения результирующей последовательности приемник передает ее дескрэмблеру, который восстанавливает исходную

последовательность на основании обратного соотношения.

Существуют другие различные алгоритмы скрэмблирования, они отличаются количеством слагаемых, дающих цифру

результирующего кода, и сдвигом между слагаемыми.

Главная проблема кодирования на основе скремблеров — синхронизация передающего (кодирующего) и принимающего

(декодирующего) устройств. При пропуске или ошибочном вставлении хотя бы одного бита вся передаваемая информация

необратимо теряется. Поэтому, в системах кодирования на основе скремблеров очень большое внимание уделяется методам синхронизации.

На практике для этих целей обычно применяется комбинация двух методов:

а) добавление в поток информации синхронизирующих битов, заранее известных приемной стороне, что позволяет ей при ненахождении

такого бита активно начать поиск синхронизации с отправителем,

б) использование высокоточных генераторов временных импульсов, что позволяет в моменты потери синхронизации производить

декодирование принимаемых битов информации «по памяти» без синхронизации.

Существуют и более простые методы борьбы с последовательностями единиц, также относимые к классу скрэмблирования.

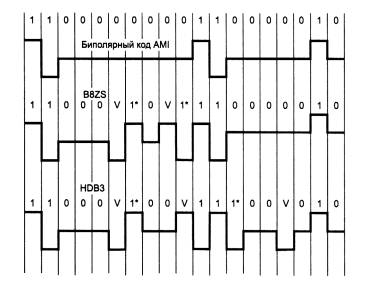

Для улучшения кода ^ Bipolar AMI используются два метода, основанные на искусственном искажении последовательности нулей запрещенными символами.

Рис. 3 Коды B8ZS и HDB3

На этом рисунке показано использование метода ^ B8ZS (Bipolar with 8-Zeros Substitution) и метода HDB3 (High-Density Bipolar 3-Zeros) для корректировки

кода AMI. Исходный код состоит из двух длинных последовательностей нулей (8- в первом случае и 5 во втором).

Код B8ZS исправляет только последовательности, состоящие из 8 нулей. Для этого он после первых трех нулей вместо оставшихся пяти нулей вставляет пять

цифр: V-1*-0-V-1*. V здесь обозначает сигнал единицы, запрещенной для данного такта полярности, то есть сигнал, не изменяющий полярность предыдущей

единицы, 1* — сигнал единицы корректной полярности, а знак звездочки отмечает тот факт, что в исходном коде в этом такте была не единица, а ноль. В

результате на 8 тактах приемник наблюдает 2 искажения — очень маловероятно, что это случилось из-за шума на линии или других сбоев передачи. Поэтому

приемник считает такие нарушения кодировкой 8 последовательных нулей и после приема заменяет их на исходные 8 нулей.

Код B8ZS построен так, что его постоянная составляющая равна нулю при любых последовательностях двоичных цифр.

Код HDB3 исправляет любые 4 подряд идущих нуля в исходной последовательности. Правила формирования кода HDB3 более сложные, чем кода B8ZS.

Каждые четыре нуля заменяются четырьмя сигналами, в которых имеется один сигнал V. Для подавления постоянной составляющей полярность сигнала

V чередуется при последовательных заменах.

Кроме того, для замены используются два образца четырехтактовых кодов. Если перед заменой исходный код содержал нечетное число единиц, то

используется последовательность 000V, а если число единиц было четным — последовательность 1*00V.

Таким образом, применение логическое кодирование совместно с потенциальным кодированием дает следующие преимущества:

Улучшенные потенциальные коды обладают достаточно узкой полосой пропускания для любых последовательностей единиц и нулей,

которые встречаются в передаваемых данных. В результате коды, полученные из потенциального путем логического кодирования,

обладают более узким спектром, чем манчестерский, даже при повышенной тактовой частоте.

Линейные блочные коды

При передаче информации по каналам связи возможны ошибки вследствие помех и искажений сигналов. Для обнаружения и

исправления возникающих ошибок используются помехоустойчивые коды. Упрощенная схема системы передачи информации

при помехоустойчивом кодировании показана на рис. 4

Кодер служит для преобразования поступающей от источника сообщений последовательности из k информационных

символов в последовательность из n cимволов кодовых комбинаций (или кодовых слов). Совокупность кодовых слов образует код.

Множество символов, из которых составляется кодовое слово, называется алфавитом кода, а число различных символов в

алфавите – основанием кода. В дальнейшем вследствие их простоты и наибольшего распространения рассматриваются главным

образом двоичные коды, алфавит которых содержит два символа: 0 и 1.

Рис. 4 Система передачи дискретных сообщений

Правило, по которому информационной последовательности сопоставляется кодовое слово, называется правилом кодирования.

Если при кодировании каждый раз формируется блок А из k информационных символов, превращаемый затем в n-символьную

кодовую комбинацию S, то код называется блочным. При другом способе кодирования информационная последовательность на

блоки не разбивается, и код называется непрерывным.

С математической точки зрения кодер осуществляет отображение множества из 2k элементов (двоичных информационных

последовательностей) в множество, состоящее из 2n элементов (двоичных последовательностей длины n). Для практики

интересны такие отображения, в результате которых получаются коды, обладающие способностью исправлять часть ошибок

и допускающие простую техническую реализацию кодирующих и декодирующих устройств.

Дискретный канал связи – это совокупность технических средств вместе со средой распространения радиосигналов, включенных

между кодером и декодером для передачи сигналов, принимающих конечное число разных видов. Для описания реальных каналов

предложено много математических моделей, с разной степенью детализации отражающих реальные процессы. Ограничимся рассмотрением

простейшей модели двоичного канала, входные и выходные сигналы которого могут принимать значения 0 и 1.

Наиболее распространено предположение о действии в канале аддитивной помехи. Пусть S=(s1,s2,…,sn)

и Y=(y1,y2,…,yn) соответственно входная и выходная последовательности двоичных символов.

Помехой или вектором ошибки называется последовательность из n символов E=(e1,e2,…,en), которую

надо поразрядно сложить с переданной последовательностью, чтобы получить принятую:

Y=S+E

Таким образом, компонента вектора ошибки ei=0 указывает на то, что 2-й символ принят правильно (yi=si),

а компонента ei=1 указывает на ошибку при приеме (yi≠si).Поэтому важной характеристикой вектора ошибки

является число q ненулевых компонентов, которое называется весом или кратностью ошибки. Кратность ошибки – дискретная случайная величина,

принимающая целочисленные значения от 0 до n.

Классификация двоичных каналов ведется по виду распределения случайного вектора E. Основные результаты теории кодирования получены в

предположении, что вероятность ошибки в одном символе не зависит ни от его номера в последовательности, ни от его значения. Такой

канал называется стационарным и симметричным. В этом канале передаваемые символы искажаются с одинаковой вероятностью

P, т.е. P(ei=1)=P, i=1,2,…,n.

Для симметричного стационарного канала распределение вероятностей векторов ошибки кратности q является биноминальным:

P(Ei)=Pq(1-P)n-q

которая показывает, что при P<0,5 вероятность β2=αj является убывающей функцией q,

т.е. в симметричном стационарном канале более вероятны ошибки меньшей кратности. Этот важный факт используется при построении

помехоустойчивых кодов, т.к. позволяет обосновать тактику обнаружения и исправления в первую очередь ошибок малой кратности.

Конечно, для других моделей канала такая тактика может и не быть оптимальной.

Декодирующее устройство (декодер) предназначено оценить по принятой последовательности Y=(y1,y2,…,yn)

значения информационных символов A‘=(a‘1,a‘2,…,a‘k,).

Из-за действия помех возможны неправильные решения. Процедура декодирования включает решение двух задач: оценивание переданного кодового

слова и формирование оценок информационных символов.

Вторая задача решается относительно просто. При наиболее часто используемых систематических кодах, кодовые слова которых содержат информационные

символы на известных позициях, все сводится к простому их стробированию. Очевидно также, что расположение информационных символов внутри кодового

слова не имеет существенного значения. Удобно считать, что они занимают первые k позиций кодового слова.

Наибольшую трудность представляет первая задача декодирования. При равновероятных информационных последовательностях ее оптимальное решение

дает метод максимального правдоподобия. Функция правдоподобия как вероятность получения данного вектора Y при передаче кодовых слов

Si, i=1,2,…,2k на основании Y=S+E определяется вероятностями появления векторов ошибок:

P(Y/Si)=P(Ei)=Pqi(1-P)n-qi

где qi – вес вектора Ei=Y+Si

Очевидно, вероятность P(Y/Si) максимальна при минимальном qi. На основании принципа максимального правдоподобия оценкой S‘ является кодовое слово,

искажение которого для превращения его в принятое слово Y имеет минимальный вес, т. е. в симметричном канале является наиболее вероятным (НВ):

S‘=Y+EHB

Если несколько векторов ошибок Ei имеют равные минимальные веса, то наивероятнейшая ошибка EHB определяется случайным выбором среди них.

В качестве расстояния между двумя кодовыми комбинациями принимают так называемое расстояние Хэмминга, которое численно равно количеству символов, в которых одна

комбинация отлична от другой, т.е. весу (числу ненулевых компонентов) разностного вектора. Расстояние Хэмминга между принятой последовательностью Y и всеми

возможными кодовыми словами 5, есть функция весов векторов ошибок Ei:

Поэтому декодирование по минимуму расстояния, когда в качестве оценки берется слово, ближайшее к принятой

последовательности, является декодированием по максимуму правдоподобия.

Таким образом, оптимальная процедура декодирования для симметричного канала может быть описана следующей последовательностью операций. По принятому

вектору Y определяется вектор ошибки с минимальным весом EHB, который затем вычитается (в двоичном канале — складывается по модулю 2) из Y:

Y→EHB→S‘=Y+EHB

Наиболее трудоемкой операцией в этой схеме является определение наи-вероятнейшего вектора ошибки, сложность которой

существенно возрастает при увеличении длины кодовых комбинаций. Правила кодирования, которые нацелены на упрощение

процедур декодирования, предполагают придание всем кодовым словам технически легко проверяемых признаков.

Широко распространены линейные коды, называемые так потому, что их кодовые слова образуют линейное

подпространство над конечным полем. Для двоичных кодов естественно использовать поле характеристики p=2.

Принадлежность принятой комбинации Y известному подпространству является тем признаком, по которому

выносится решение об отсутствии ошибок (EHB=0).

Так как по данному коду все пространство последовательностей длины n разбивается на смежные классы,

то для каждого смежного класса можно заранее определить вектор ошибки минимального веса,

называемый лидером смежного класса. Тогда задача декодера состоит в определении номера смежного класса,

которому принадлежит Y, и формировании лидера этого класса.

Проблемы информационной безопасности требуют изучения и решения ряда теоретических и практических задач при информационном взаимодействии абонентов систем. В нашей доктрине информационной безопасности формулируется триединая задача обеспечения целостности, конфиденциальности и доступности информации. Представляемые здесь статьи посвящаются рассмотрению конкретных вопросов ее решения в рамках разных государственных систем и подсистем. Ранее автором были рассмотрены в 5 статьях вопросы обеспечения конфиденциальности сообщений средствами государственных стандартов. Общая концепция системы кодирования также приводилась мной ранее.

Введение

По основному своему образованию я не математик, но в связи с читаемыми мной дисциплинами в ВУЗе пришлось в ней дотошно разбираться. Долго и упорно читал классические учебники ведущих наших Университетов, пятитомную математическую энциклопедию, множество тонких популярных брошюр по отдельным вопросам, но удовлетворения не возникало. Не возникало и глубокое понимание прочитанного.

Вся математическая классика ориентирована, как правило, на бесконечный теоретический случай, а специальные дисциплины опираются на случай конечных конструкций и математических структур. Отличие подходов колоссальное, отсутствие или недостаток хороших полных примеров — пожалуй главный минус и недостаток вузовских учебников. Очень редко существует задачник с решениями для начинающих (для первокурсников), а те, что имеются, грешат пропусками в объяснениях. В общем я полюбил букинистические магазины технической книги, благодаря чему пополнилась библиотека и в определенной мере багаж знаний. Читать довелось много, очень много, но «не заходило».

Этот путь привел меня к вопросу, а что я уже могу самостоятельно делать без книжных «костылей», имея перед собой только чистый лист бумаги и карандаш с ластиком? Оказалось совсем немного и не совсем то, что было нужно. Пройден был сложный путь бессистемного самообразования. Вопрос был такой. Могу ли я построить и объяснить, прежде всего себе, работу кода, обнаруживающего и исправляющего ошибки, например, код Хемминга, (7, 4)-код?

Известно, что код Хемминга широко используется во многих прикладных программах в области хранения и обмена данными, особенно в RAID; кроме того, в памяти типа ECC и позволяет «на лету» исправлять однократные и обнаруживать двукратные ошибки.

Информационная безопасность. Коды, шифры, стегосообщения

Информационное взаимодействие путем обмена сообщениями его участников должно обеспечиваться защитой на разных уровнях и разнообразными средствами как аппаратными так и программными. Эти средства разрабатываются, проектируются и создаются в рамках определенных теорий (см. рис.А) и технологий, принятых международными договоренностями об OSI/ISO моделях.

Защита информации в информационных телекоммуникационных системах (ИТКС) становится практически основной проблемой при решении задач управления, как в масштабе отдельной личности – пользователя, так и для фирм, объединений, ведомств и государства в целом. Из всех аспектов защиты ИТКС в этой статье будем рассматривать защиту информации при ее добывании, обработке, хранении и передаче в системах связи.

Уточняя далее предметную область, остановимся на двух возможных направлениях, в которых рассматриваются два различных подхода к защите, представлению и использованию информации: синтаксическом и семантическом. На рисунке используются сокращения: кодек–кодер-декодер; шидеш – шифратор-дешифратор; скриз – скрыватель – извлекатель.

Рисунок А – Схема основных направлений и взаимосвязи теорий, направленных на решение задач защиты информационного взаимодействия

Синтаксические особенности представления сообщений позволяют контролировать и обеспечивать правильность и точность (безошибочность, целостность) представления при хранении, обработке и особенно при передаче информации по каналам связи. Здесь главные задачи защиты решаются методами кодологии, ее большой части — теории корректирующих кодов.

Семантическая (смысловая) безопасность сообщений обеспечивается методами криптологии, которая средствами криптографии позволяет защитить от овладения содержанием информации потенциальным нарушителем. Нарушитель при этом может скопировать, похитить, изменить или подменить, или даже уничтожить сообщение и его носитель, но он не сможет получить сведений о содержании и смысле передаваемого сообщения. Содержание информации в сообщении останется для нарушителя недоступным. Таким образом, предметом дальнейшего рассмотрения будет синтаксическая и семантическая защита информации в ИТКС. В этой статье ограничимся рассмотрением только синтаксического подхода в простой, но весьма важной его реализации корректирующим кодом.

Сразу проведу разграничительную линию в решении задач информационной безопасности:

теория кодологии призвана защищать информацию (сообщения) от ошибок (защита и анализ синтаксиса сообщений) канала и среды, обнаруживать и исправлять ошибки;

теория криптологии призвана защищать информацию от несанкционированного доступа к ее семантике нарушителя (защита семантики, смысла сообщений);

теория стеганологии призвана защищать факт информационного обмена сообщениями, а также обеспечивать защиту авторского права, персональных данных (защита врачебной тайны).

В общем «поехали». По определению, а их довольно много, понять что есть код очень даже не просто. Авторы пишут, что код — это алгоритм, отображение и ещё что-то. О классификации кодов я не буду здесь писать, скажу только, что (7, 4)-код блоковый.

В какой-то момент до меня дошло, что код — это кодовые специальные слова, конечное их множество, которыми заменяют специальными алгоритмами исходный текст сообщения на передающей стороне канала связи и которые отправляются по каналу получателю. Замену осуществляет устройство-кодер, а на приемной стороне эти слова распознает устройство-декодер.

Поскольку роль сторон переменчива оба этих устройства объединяют в одно и называют сокращенно кодек (кодер/декодер), и устанавливают на обоих концах канала. Дальше, раз есть слова, есть и алфавит. Алфавит — это два символа {0, 1}, в технике массово используются блоковые двоичные коды. Алфавит естественного языка (ЕЯ) — множество символов — букв, заменяющих при письме звуки устной речи. Здесь не будем углубляться в иероглифическую письменность в слоговое или узелковое письмо.

Алфавит и слова — это уже язык, известно, что естественные человеческие языки избыточны, но что это означает, где обитает избыточность языка трудно сказать, избыточность не очень хорошо организована, хаотична. При кодировании, хранении информации избыточность стремятся уменьшить, пример, архиваторы, код Морзе и др.

Ричард Хемминг, наверное, раньше других понял, что если избыточность не устранять, а разумно организовать, то ее можно использовать в системах связи для обнаружения ошибок и автоматического их исправления в кодовых словах передаваемого текста. Он понял, что все 128 семиразрядных двоичных слов могут использоваться для обнаружения ошибок в кодовых словах, которые образуют код — подмножество из 16 семиразрядных двоичных слов. Это была гениальная догадка.

До изобретения Хемминга ошибки приемной стороной тоже обнаруживались, когда декодированный текст не читался или получалось не совсем то, что нужно. При этом посылался запрос отправителю сообщения повторить блоки определенных слов, что, конечно, было весьма неудобно и тормозило сеансы связи. Это было большой не решаемой десятилетиями проблемой.

Построение (7, 4)-кода Хемминга

Вернемся к Хеммингу. Слова (7, 4)-кода образованы из 7 разрядов С j =

, j = 0(1)15, 4-информационные и 3-проверочные символа, т.е. по существу избыточные, так как они не несут информации сообщения. Эти три проверочных разряда удалось представить линейными функциями 4-х информационных символов в каждом слове, что и обеспечило обнаружение факта ошибки и ее места в словах, чтобы внести исправление. А (7, 4)-код получил новое прилагательное и стал линейным блоковым двоичным.

Линейные функциональные зависимости (правила (*)) вычислений значений символов

имеют следующий вид:

Исправление ошибки стало очень простой операцией — в ошибочном разряде определялся символ (ноль или единица) и заменялся другим противоположным 0 на 1 или 1 на 0.

Сколько же различных слов образуют код? Ответ на этот вопрос для (7, 4)-кода получается очень просто. Раз имеется лишь 4 информационных разряда, а их разнообразие при заполнении символами имеет

= 16 вариантов, то других возможностей просто нет, т. е. код состоящий всего из 16 слов, обеспечивает представление этими 16-ю словами всю письменность всего языка.

Информационные части этих 16 слов получают нумерованный вид №

(

):

0=0000; 4= 0100; 8=1000; 12=1100;

1=0001; 5= 0101; 9=1001; 13=1101;

2=0010; 6= 0110; 10=1010; 14=1110;

3=0011; 7= 0111; 11=1011; 15=1111.

Каждому из этих 4-разрядных слов необходимо вычислить и добавить справа по 3 проверочных разряда, которые вычисляются по правилам (*). Например, для информационного слова №6 равного 0110 имеем

и вычисления проверочных символов дают для этого слова такой результат:

Шестое кодовое слово при этом приобретает вид:

Таким же образом необходимо вычислить проверочные символы для всех 16-и кодовых слов. Подготовим для слов кода 16-строчную таблицу К и последовательно будем заполнять ее клетки (читателю рекомендую проделать это с карандашом в руках).

Таблица К – кодовые слова Сj, j = 0(1)15, (7, 4) – кода Хемминга

Описание таблицы: 16 строк — кодовые слова; 10 колонок: порядковый номер, десятичное представление кодового слова, 4 информационных символа, 3 проверочных символа, W-вес кодового слова равен числу ненулевых разрядов (≠ 0). Заливкой выделены 4 кодовых слова-строки — это базис векторного подпространства. Собственно, на этом все — код построен.

Таким образом, в таблице получены все слова (7, 4) — кода Хемминга. Как видите это было не очень сложно. Далее речь пойдет о том, какие идеи привели Хемминга к такому построению кода. Мы все знакомы с кодом Морзе, с флотским семафорным алфавитом и др. системами построенными на разных эвристических принципах, но здесь в (7, 4)-коде используются впервые строгие математические принципы и методы. Рассказ будет как раз о них.

Математические основы кода. Высшая алгебра

Подошло время рассказать какая Р.Хеммингу пришла идея открытия такого кода. Он не питал особых иллюзий о своем таланте и скромно формулировал перед собой задачу: создать код, который бы обнаруживал и исправлял в каждом слове одну ошибку (на деле обнаруживать удалось даже две ошибки, но исправлялась лишь одна из них). При качественных каналах даже одна ошибка — редкое событие. Поэтому замысел Хемминга все-таки в масштабах системы связи был грандиозным. В теории кодирования после его публикации произошла революция.

Это был 1950 год. Я привожу здесь свое простое (надеюсь доступное для понимания) описание, которого не встречал у других авторов, но как оказалось, все не так просто. Потребовались знания из многочисленных областей математики и время, чтобы все глубоко осознать и самому понять, почему это так сделано. Только после этого я смог оценить ту красивую и достаточно простую идею, которая реализована в этом корректирующем коде. Время я в основном, потратил на разбирательство с техникой вычислений и теоретическим обоснованием всех действий, о которых здесь пишу.

Создатели кодов, долго не могли додуматься до кода, обнаруживающего и исправляющего две ошибки. Идеи, использованные Хеммингом, там не срабатывали. Пришлось искать, и нашлись новые идеи. Очень интересно! Захватывает. Для поиска новых идей потребовалось около 10 лет и только после этого произошел прорыв. Коды, обнаруживающие произвольное число ошибок, были получены сравнительно быстро.

Векторные пространства, поля и группы. Полученный (7, 4)-код (Таблица К) представляет множество кодовых слов, являющихся элементами векторного подпространства (порядка 16, с размерностью 4), т.е. частью векторного пространства размерности 7 с порядком

Из 128 слов в код включены лишь 16, но они попали в состав кода не просто так.

Во-первых, они являются подпространством со всеми вытекающими отсюда свойствами и особенностями, во-вторых, кодовые слова являются подгруппой большой группы порядка 128, даже более того, аддитивной подгруппой конечного расширенного поля Галуа GF(

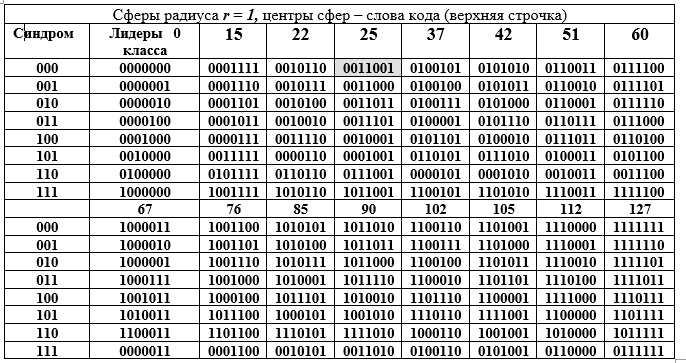

) степени расширения n = 7 и характеристики 2. Эта большая подгруппа раскладывается в смежные классы по меньшей подгруппе, что хорошо иллюстрируется следующей таблицей Г. Таблица разделена на две части: верхняя и нижняя, но читать следует как одну длинную. Каждый смежный класс (строка таблицы) — элемент факторгруппы по эквивалентности составляющих.

Таблица Г – Разложение аддитивной группы поля Галуа GF () в смежные классы (строки таблицы Г) по подгруппе 16 порядка.

Столбцы таблицы – это сферы радиуса 1. Левый столбец (повторяется) – синдром слова (7, 4)-кода Хемминга, следующий столбец — лидеры смежного класса. Раскроем двоичное представление одного из элементов (25-го выделен заливкой) факторгруппы и его десятичное представление:

Техника получение строк таблицы Г. Элемент из столбца лидеров класса суммируется с каждым элементом из заголовка столбца таблицы Г (суммирование выполняется для строки лидера в двоичном виде по mod2). Поскольку все лидеры классов имеют вес W=1, то все суммы отличаются от слова в заголовке столбца только в одной позиции (одной и той же для всей строки, но разных для столбца). Таблица Г имеет замечательную геометрическую интерпретацию. Все 16 кодовых слов представляются центрами сфер в 7-мерном векторном пространстве. Все слова в столбце от верхнего слова отличаются в одной позиции, т. е. лежат на поверхности сферы с радиусом r =1.

В этой интерпретации скрывается идея обнаружения одной ошибки в любом кодовом слове. Работа идет со сферами. Первое условие обнаружения ошибки — сферы радиуса 1 не должны касаться или пересекаться. Это означает, что центры сфер удалены друг от друга на расстояние 3 или более. При этом сферы не только не пересекаются, но и не касаются одна другой. Это требование для однозначности решения: какой сфере отнести полученное на приемной стороне декодером ошибочное (не кодовое одно из 128 -16 = 112) слово.

Второе — все множество 7-разрядных двоичных слов из 128 слов равномерно распределено по 16 сферам. Декодер может получить слово лишь из этого множества 128-ми известных слов с ошибкой или без нее. Третье — приемная сторона может получить слово без ошибки или с искажением, но всегда принадлежащее одной из 16-и сфер, которая легко определяется декодером. В последней ситуации принимается решение о том, что послано было кодовое слово — центр определенной декодером сферы, который нашел позицию (пересечение строки и столбца) слова в таблице Г, т. е номера столбца и строки.

Здесь возникает требование к словам кода и к коду в целом: расстояние между любыми двумя кодовыми словами должно быть не менее трех, т. е. разность для пары кодовых слов, например, Сi = 85=

=1010101; Сj = 25=

= 0011001 должна быть не менее 3; 85 — 25 = 1010101 — 0011001 =1001100 = 76, вес слова-разности W(76) = 3. (табл. Д заменяет вычисления разностей и сумм). Здесь под расстоянием между двоичными словами-векторами понимается количество не совпадающих позиций в двух словах. Это расстояние Хемминга, которое стало повсеместно использоваться в теории, и на практике, так как удовлетворяет всем аксиомам расстояния.

Замечание. (7, 4)-код не только линейный блоковый двоичный, но он еще и групповой, т. е. слова кода образуют алгебраическую группу по сложению. Это означает, что любые два кодовых слова при суммировании снова дают одно из кодовых слов. Только это не обычная операция суммирования, выполняется сложение по модулю два.

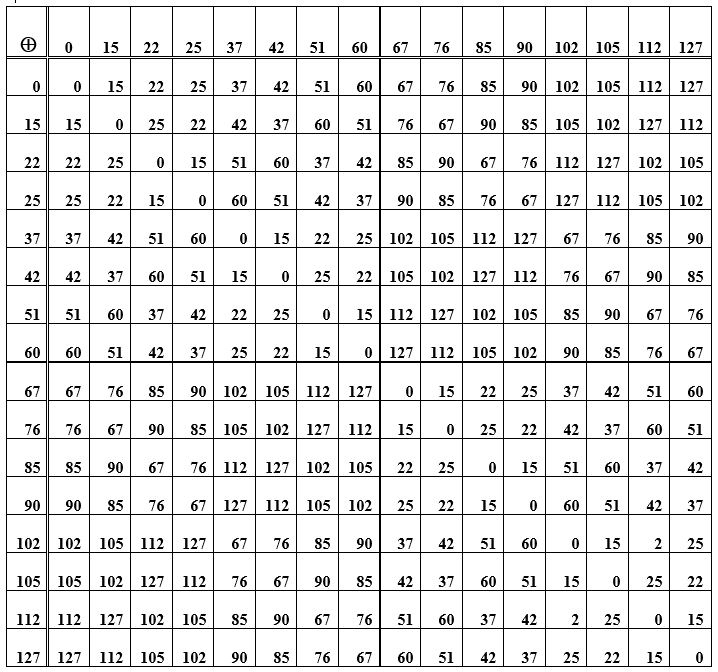

Таблица Д — Сумма элементов группы (кодовых слов), используемой для построения кода Хемминга

Сама операция суммирования слов ассоциативна, и для каждого элемента в множестве кодовых слов имеется противоположный ему, т. е. суммирование исходного слова с противоположным дает нулевое значение. Это нулевое кодовое слово является нейтральным элементом в группе. В таблице Д- это главная диагональ из нулей. Остальные клетки (пересечения строка/столбец) — это номера-десятичные представления кодовых слов, полученные суммированием элементов из строки и столбца.При перестановке слов местами (при суммировании) результат остается прежним, более того, вычитание и сложение слов имеют одинаковый результат. Дальше рассматривается система кодирования/декодирования, реализующая синдромный принцип.

Применение кода. Кодер

Кодер размещается на передающей стороне канала и им пользуется отправитель сообщения. Отправитель сообщения (автор) формирует сообщение в алфавите естественного языка и представляет его в цифровом виде. (Имя символа в ASCII-соде и в двоичном виде).

Тексты удобно формировать в файлах для ПК с использованием стандартной клавиатуры (ASCII — кодов). Каждому символу (букве алфавита) соответствует в этой кодировке октет бит (восемь разрядов). Для (7, 4)- кода Хемминга, в словах которого только 4 информационных символа, при кодировании символа клавиатуры на букву требуется два кодовых слова, т.е. октет буквы разбивается на два информационных слова естественного языка (ЕЯ) вида

.

Пример 1. Необходимо передать слово «цифра» в ЕЯ. Входим в таблицу ASCII-кодов, буквам соответствуют: ц –11110110, и –11101000, ф – 11110100, р – 11110000, а – 11100000 октеты. Или иначе в ASCII — кодах слово «цифра» = 1111 0110 1110 1000 1111 0100 1111 0000 1110 0000

с разбивкой на тетрады (по 4 разряда). Таким образом, кодирование слова «цифра» ЕЯ требует 10 кодовых слов (7, 4)-кода Хемминга. Тетрады представляют информационные разряды слов сообщения. Эти информационные слова (тетрады) преобразуются в слова кода (по 7 разрядов) перед отправкой в канал сети связи. Выполняется это путем векторно-матричного умножения: информационного слова на порождающую матрицу. Плата за удобства получается весьма дорого и длинно, но все работает автоматически и главное — сообщение защищается от ошибок.

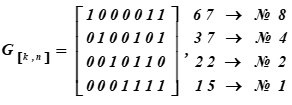

Порождающая матрица (7, 4)-кода Хемминга или генератор слов кода получается выписыванием базисных векторов кода и объединением их в матрицу. Это следует из теоремы линейной алгебры: любой вектор пространства (подпространства) является линейной комбинацией базисных векторов, т.е. линейно независимых в этом пространстве. Это как раз и требуется — порождать любые векторы (7-разрядные кодовые слова) из информационных 4-разрядных.

Порождающая матрица (7, 4, 3)-кода Хемминга или генератор слов кода имеет вид:

Справа указаны десятичные представления кодовых слов Базиса подпространства и их порядковые номера в таблице К

№ i строки матрицы — это слова кода, являющиеся базисом векторного подпространства.

Пример кодирования слов информационных сообщений (порождающая матрица кода выстраивается из базисных векторов и соответствует части таблицы К). В таблице ASCII-кода берем букву ц = <1111 0110>.

Информационные слова сообщения имеют вид:

.

Это половины символа (ц). Для (7, 4)-кода, определенного ранее, требуется найти кодовые слова, соответствующее информационному слову-сообщению (ц) из 8-и символов в виде:

.

Чтобы превратить эту букву–сообщение (ц) в кодовые слова u, каждую половинку буквы-сообщения i умножают на порождающую матрицу G[k, n] кода (матрица для таблицы К):

Получили два кодовых слова с порядковыми номерами 15 и 6.

Покажем детальное формирование нижнего результата №6 – кодового слова (умножение строки информационного слова на столбцы порождающей матрицы); суммирование по (mod2)

<0110> ∙ <1000> = 0∙1 +1∙0 + 1∙0 + 0∙0 = 0(mod2);

<0110> ∙ <0100> = 0∙0 +1∙1 + 1∙0 + 0∙0 = 1(mod2);

<0110> ∙ <0010> = 0∙0 +1∙0 + 1∙1 + 0∙0 = 1(mod2);

<0110> ∙ <0001> = 0∙0 +1∙0 + 1∙0 + 0∙1 = 0(mod2);

<0110> ∙ <0111> = 0∙0 +1∙1 + 1∙1 + 0∙1 = 0(mod2);

<0110> ∙ <1011> = 0∙1 +1∙0 + 1∙1 + 0∙1 = 1(mod2);

<0110> ∙ <1101> = 0∙1 +1∙1 + 1∙0 + 0∙1 = 1(mod2).

Получили в результате перемножения пятнадцатое и шестое слова из таблицы К. Первые четыре разряда в этих кодовых словах (результатах умножения) представляют информационные слова. Они имеют вид:

, (в таблице ASCII это только половины буквы ц). Для кодирующей матрицы выбраны в качестве базисных векторов в таблице К совокупности слов с номерами: 1, 2, 4, 8. В таблице они выделены заливкой. Тогда для этой таблицы К кодирующая матрица получит вид G[k,n].

В результате перемножения получили 15 и 6 слова таблицы К кода.

Применение кода. Декодер

Декодер размещается на приемной стороне канала там, где находится получатель сообщения. Назначение декодера состоит в предоставлении получателю переданного сообщения в том виде, в котором оно существовало у отправителя в момент отправления, т.е. получатель может воспользоваться текстом и использовать сведения из него для своей дальнейшей работы.

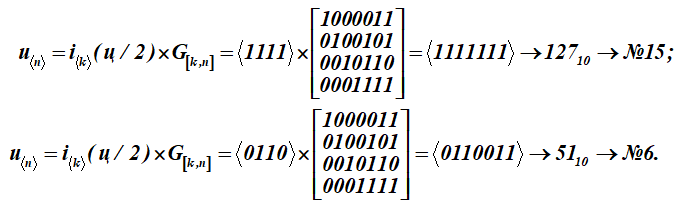

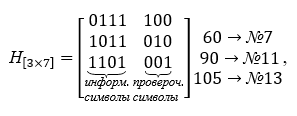

Основной задачей декодера является проверка того, является ли полученное слово (7 разрядов) тем, которое было отправлено на передающей стороне, не содержит ли слово ошибок. Для решения этой задачи для каждого полученного слова декодером путем умножения его на проверочную матрицу Н[n-k, n] вычисляется короткий вектор-синдром S (3 разряда).

Для слов, которые являются кодовыми, т. е. не содержат ошибок, синдром всегда принимает нулевое значение S =<000>. Для слова с ошибкой синдром не нулевой S ≠ 0. Значение синдрома позволяет обнаружить и локализовать положение ошибки с точностью до разряда в принятом на приемной стороне слове, и декодер может изменить значение этого разряда. В проверочной матрице кода декодер находит столбец, совпадающий со значением синдрома, и порядковый номер этого столбца принимает равным искаженному ошибкой разряду. После этого для двоичных кодов декодером выполняется изменение этого разряда – просто замена на противоположное значение, т. е. единицу заменяют нулем, а нуль – единицей.

Рассматриваемый код является систематическим, т. е. символы информационного слова размещаются подряд в старших разрядах кодового слова. Восстановление информационных слов выполняется простым отбрасыванием младших (проверочных) разрядов, число которых известно. Далее используется таблица ASCII-кодов в обратном порядке: входом являются информационные двоичные последовательности, а выходом – буквы алфавита естественного языка. Итак, (7, 4)-код систематический, групповой, линейный, блочный, двоичный.

Основу декодера образует проверочная матрица Н[n-k, n], которая содержит число строк, равное числу проверочных символов, а столбцами все возможные, кроме нулевого, столбцы из трех символов

. Проверочная матрица строится из слов таблицы К, они выбираются так, чтобы быть ортогональными к кодирующей матрице, т.е. их произведение — нулевая матрица. Проверочная матрица получает следующий вид в операциях умножения она транспонируется. Для конкретного примера проверочная матрица Н[n-k, n] приведена ниже:

Видим, что произведение порождающей матрицы на проверочную в результате дает нулевую матрицу.

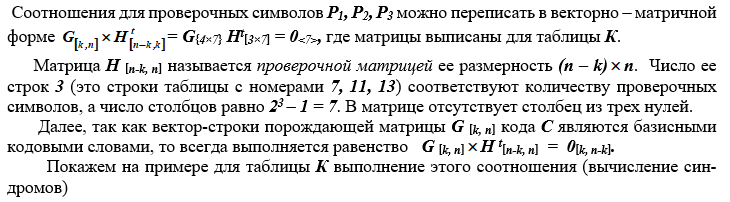

Пример 2. Декодирование слова кода Хемминга без ошибки (е<7> =<0000000>).

Пусть на приемном конце канала приняты слова №7→60 и №13→105 из таблицы К,

u<7> + е<7> = <0 1 1 1 1 0 0 > + <0 0 0 0 0 0 0>,

где ошибка отсутствует, т. е. имеет вид е<7> = <0 0 0 0 0 0 0>.

В результате вычисленный синдром имеет нулевое значение, что подтверждает отсутствие ошибки в словах кода.

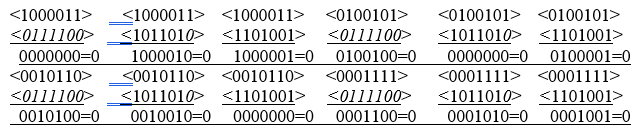

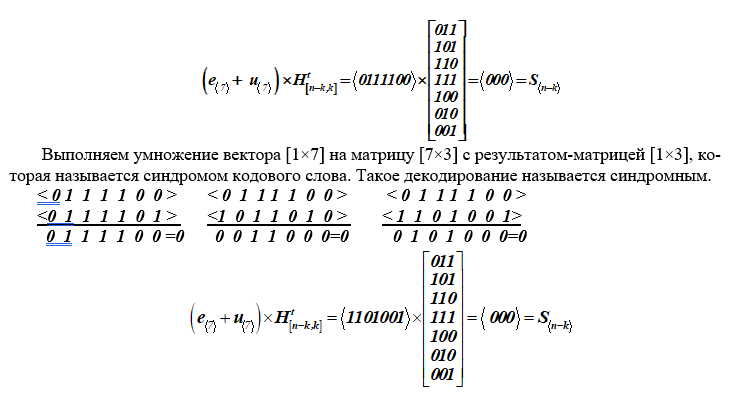

Пример 3. Обнаружение одной ошибки в слове, полученном на приемном конце канала (таблица К).

А) Пусть требуется передать 7 – е кодовое слово, т.е.

u<7> = <0 1 1 1 1 0 0> и в одном третьем слева разряде слова, допущена ошибка. Тогда она суммируется по mod2 с 7-м передаваемым по каналу связи кодовым словом

u<7> + е<7> = <0 1 1 1 1 0 0 > + <0 0 1 0 0 0 0> = <0 1 0 1 1 0 0>,

где ошибка имеет вид е<7> = <0 0 1 0 0 0 0>.

Установление факта искажения кодового слова выполняется умножением полученного искаженного слова на проверочную матрицу кода. Результатом такого умножения будет вектор, называемый синдромом кодового слова.

Выполним такое умножение для наших исходных (7-го вектора с ошибкой) данных.

В результате такого умножения на приемном конце канала получили вектор-синдром S<n-k>, размерность которого (n–k). Если синдром S<3>= <0,0,0> нулевой, то делается вывод о том, что принятое на приемной стороне слово принадлежит коду С и передано без искажений. Если синдром не равен нулю S<3> ≠ <0,0,0>, то его значение указывает на наличие ошибки и ее место в слове. Искаженный разряд соответствует номеру позиции столбца матрицы Н[n-k, n], совпадающего с синдромом. После этого искаженный разряд исправляется, и полученное слово обрабатывается декодером далее. На практике для каждого принятого слова сразу вычисляется синдром и при наличии ошибки, она автоматически устраняется.

Итак, при вычислениях получен синдром S=<110> для обоих слов одинаковый. Смотрим на проверочную матрицу и отыскиваем в ней столбец, совпадающий с синдромом. Это третий слева столбец. Следовательно, ошибка допущена в третьем слева разряде, что совпадает с условиями примера. Этот третий разряд изменяется на противоположное значение и мы вернули принятые декодером слова к виду кодовых. Ошибка обнаружена и исправлена.

Вот собственно и все, именно так устроен и работает классический (7, 4)-код Хемминга.

Здесь не рассматриваются многочисленные модификации и модернизации этого кода, так как важны не они, а те идеи и их реализации, которые в корне изменили теорию кодирования, и как следствие, системы связи, обмена информацией, автоматизированные системы управления.

Заключение

В работе рассмотрены основные положения и задачи информационной безопасности, названы теории, призванные решать эти задачи.

Задача защиты информационного взаимодействия субъектов и объектов от ошибок среды и от воздействий нарушителя относится к кодологии.

Рассмотрен в деталях (7, 4)-код Хемминга, положивший начало нового направлению в теории кодирования — синтеза корректирующих кодов.

Показано применение строгих математических методов, используемых при синтезе кода.

Приведены примеры иллюстрирующие работоспособность кода.

Литература

Питерсон У., Уэлдон Э. Коды, исправляющие ошибки: Пер. с англ. М.: Мир, 1976, 594 c.

Блейхут Р. Теория и практика кодов, контролирующих ошибки. Пер.с англ. М.: Мир, 1986, 576 с.

Построение кодов

Хемминга базируется на принципе проверки

на чётность веса W

(числа единичных символов) в информационной

группе кодового блока.

Поясним идею

проверки на чётность на примере

простейшего корректирующего кода,

который так и называется, кодом с

проверкой на чётность или кодом с

проверкой по паритету (равенству).

В таком коде к

кодовым комбинациям безызбыточного

первичного двоичного k-разрядного

кода добавляется один дополнительный

разряд (символ проверки на чётность,

называемый проверочным, или контрольным).

Если число символов «1» в исходной

кодовой комбинации чётное, то в

дополнительном разряде формируют

контрольный символ «0», а если число

символов «1» нечётное, то в дополнительном

разряде формируют символ «1». В результате

общее число символов «1» в любой

передаваемой кодовой комбинации всегда

будет чётным.

Таким образом,

правило формирования проверочного

символа cводится

к следующему:

r1

= i1

i2

. . .

ik,

где i

–

соответствующий информационный символ

(0 или 1); k –

общее их число, а под операцией

здесь и далее понимается сложение по

модулю 2.

Очевидно, что

добавление дополнительного разряда

увеличивает общее число возможных

комбинаций вдвое по сравнению с числом

комбинаций исходного первичного кода,

а условие чётности разделяет все

комбинации на разрешённые и неразрешённые.

Код с проверкой на чётность позволяет

обнаруживать одиночную ошибку при

приёме кодовой комбинации, так как такая

ошибка нарушает условие чётности,

переводя разрешённую комбинацию в

запрещённую.

Критерием

правильности принятой комбинации

является равенство нулю результата S

суммирования по модулю 2 всех n

символов кода, включая проверочный

символ ri.

При наличии одиночной ошибки S

принимает значение 1:

S = r1

i1

i2

. . .

ik

= 0

– ошибки

нет;

S

= r1

i1

i2

. . .

ik

= 1

– однократная ошибка.

Этот код является

(k + 1,

k)-кодом, или

(n, n — 1)-кодом.

Минимальное расстояние кода равно двум

(dmin

= 2), и,

следовательно, никакие ошибки не могут

быть исправлены. Простой код с проверкой

на чётность может использоваться только

для обнаружения (но не исправления)

однократных ошибок.

Увеличивая число

дополнительных проверочных разрядов

и формируя по определённым правилам

проверочные символы r,

равные 0 или 1, можно усилить корректирующие

свойства кода так, чтобы он позволял не

только обнаруживать, но и исправлять

ошибки. На этом и основано построение

кодов Хемминга.

Рассмотрим эти коды, позволяющие

исправлять одиночную ошибку, с помощью

непосредственного описания. Для каждого

числа проверочных символов r

= 3, 4, 5…

существует классический код Хемминга

с маркировкой

(n,

k)

= (2r

– 1,

2r

– 1

— r),

(4.24)

т. е. – (7,4),

(15,11), (31,26).

При других значениях

числа информационных символов k

получаются так

называемые усечённые

(укороченные) коды Хемминга. Так, для

международного телеграфного кода МТК-2,

имеющего 5 информационных символов,

потребуется использование корректирующего

кода (9,5), являющегося усечённым от

классического кода Хемминга (15,11), так

как число символов в этом коде уменьшается

(укорачивается) на 6. Для примера рассмотрим

классический код Хемминга (7,4), который

можно сформировать и описать с помощью

кодера, представленного на рис. 4.2.

Рис. 4.2

В простейшем

варианте при заданных четырёх (k

= 4) информационных

символах (i1,

i2,

i3,

i4)

будем полагать, что они сгруппированы

в начале кодового слова, хотя это и не

обязательно. Дополним эти информационные

символы тремя проверочными символами

(r

= 3), задавая их следующими равенствами

проверки на чётность, которые определяются

соответствующими алгоритмами

r1

= i1

i2

i3;

r2

= i2

i3

i4;

r3

= i1

i2

i4,

где знак «»

означает сложение по модулю 2.

На рис. 4.3 приведена

схема декодера для (7,4)-кода Хемминга,

на вход которого поступает кодовое

слово:

V =

(i′1,

i′2,

i′3,

i′4

,

r′1,

r′2,

r

′3).

Апостроф означает,

что любой символ слова может быть искажён

помехой в канале передачи.

Рис. 4.3

В декодере, в режиме

исправления ошибок, строится

последовательность:

s1

= r1’

i1’

i2’

i3’;

s2

= r2’

i2’

i3’

i4’;

s3

= r3’

i1’

i2’

i4’.

Трёхсимвольная

последовательность (s1,

s2,

s3)

называется синдромом. Термин «синдром»

используется и в медицине, где он

обозначает сочетание признаков,

характерных для определённого заболевания.

В данном случае синдром S

= (s1,

s2,

s3)

представляет собой сочетание результатов

проверки на чётность соответствующих

символов кодовой группы и характеризует

определённую конфигурацию ошибок

(шумовой вектор).

Кодовые слова кода

Хемминга для k

= 4 и r

= 3 приведены в табл. 4.1.

Число возможных

синдромов определяется выражением

S = 2r.

(4.25)

При числе проверочных

символов r

= 3, имеется восемь возможных синдромов

(23

= 8). Нулевой синдром (000) указывает на то,

что ошибки при приёме отсутствуют или

не обнаружены. Всякому ненулевому

синдрому соответствует определённая

конфигурация ошибок, которая и

исправляется. Классические коды Хемминга

(4.20) имеют число синдромов, точно равное

их необходимому числу, позволяют

исправить все однократные ошибки в

любом информативном и проверочном

символах и включают один нулевой синдром.

Такие коды называются плотноупакованными.

Таблица 4.1

|

k |

r |

|||||

|

i1 |

i2 |

i3 |

i4 |

r1 |

r2 |

r3 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Усечённые коды

являются неплотноупакованными, так как

число синдромов у них превышает

необходимое. Так, в коде (9,5) при четырёх

проверочных символах число синдромов

будет равно 24

= 16, в то время как необходимо всего 10.

Лишние 6 синдромов свидетельствуют о

неполной упаковке кода (9,5).

Для рассматриваемого

кода (7,4) в табл. 4.2 представлены ненулевые

синдромы и соответствующие конфигурации

ошибок.

Таблица 4.2

|

Синдром |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|

Конфигурация |

0000001 |

0000010 |

0001000 |

0000100 |

1000000 |

0010000 |

0100000 |

|

Ошибка |

r3 |

r2 |